# A 12b 50MS/s 0.18µm CMOS SAR ADC Based on Highly Linear C-R Hybrid DAC

Je-Min Jeon, Yong-Tae Kim, Jun-Sang Park, and Seung-Hoon Lee Department of Electronic Engineering, Sogang University, Seoul, Korea

#### INTRODUCTION

- → Required ADC specifications for intelligent semiconductor system applications:

- ➤ Resolution: 12b ➤ Sampling rate: 50MS/s

- ➤ Small chip area and low power consumption in CMOS process

- → Conventional monotonic switching of SAR ADCs:

➤ Non-competitive switching power of a DAC

- ➤ Simple circuit topology and SAR operation with top plate sampling

- ➤ Dynamic offset caused by V<sub>CM</sub> variations of a DAC output

- → Proposed 12b 50MS/s SAR ADC based on a 0.18µm CMOS process :

- ➤ Composite switching composed of V<sub>CM</sub> and monotonic switching in sequence

- ➤ Composite switching simultaneously to minimize switching power of a DAC and dynamic offset caused by V<sub>CM</sub> variations of a DAC output

- ➤ Back-end 5b R-string for 5 LSBs combined with a unit C-array in the DAC for small chip area

- ➤ Input-range scaling to match an input range exactly to the reference voltage range without extra or dummy capacitors

SOGANG UNIVERSITY, SEOUL, KOREA

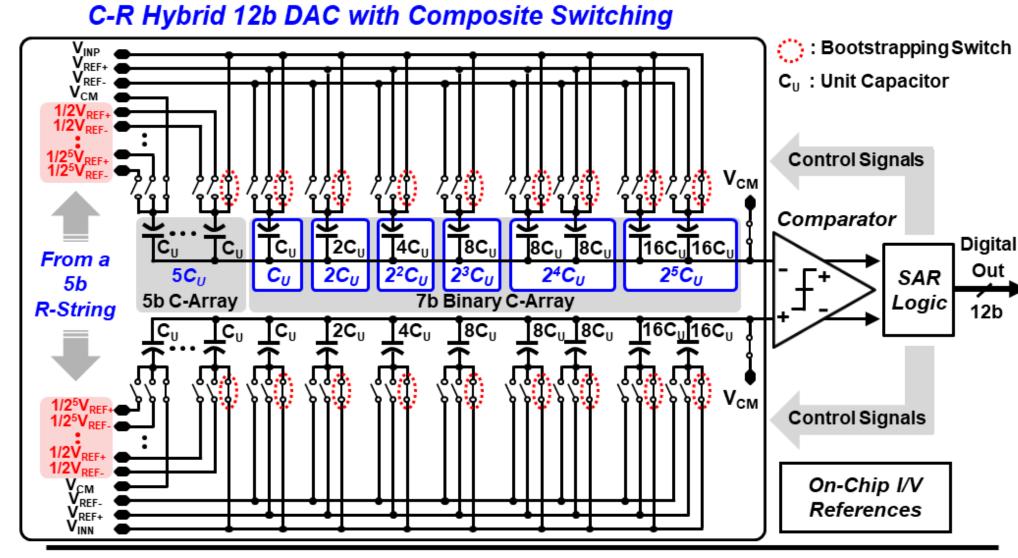

#### PROPOSED 12b 50MS/s SAR ADC

SOGANG UNIVERSITY, SEOUL, KOREA

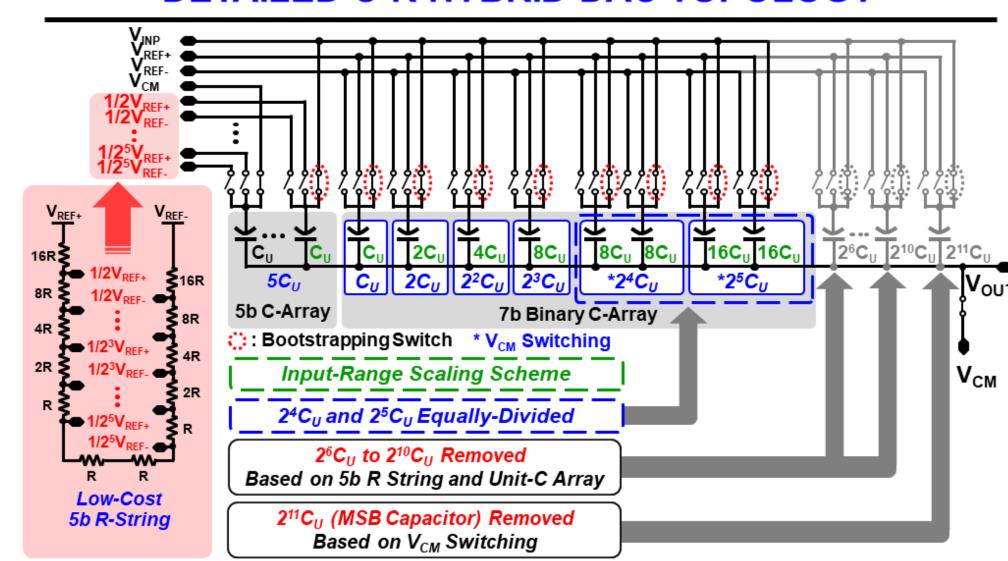

#### **DETAILED C-R HYBRID DAC TOPOLOGY**

SOGANG UNIVERSITY, SEOUL, KOREA

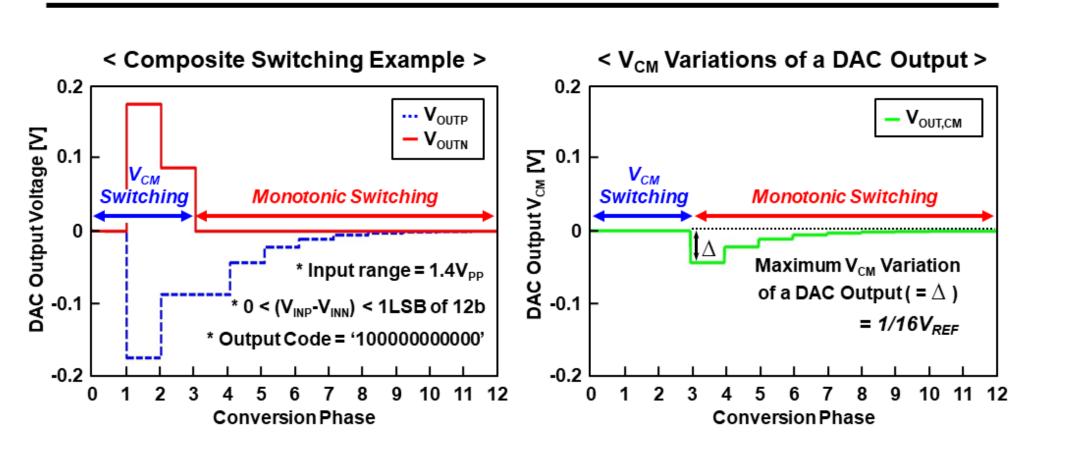

## PROPOSED COMPOSITE SWITCHING

- $\, ullet \,$  Composite switching composed of  $V_{\text{CM}}$  and monotonic switching in a consecutive order

- → V<sub>CM</sub> variations of a DAC output guaranteed within 1/16V<sub>REF</sub> with composite switching

SOGANG UNIVERSITY, SEOUL, KOREA

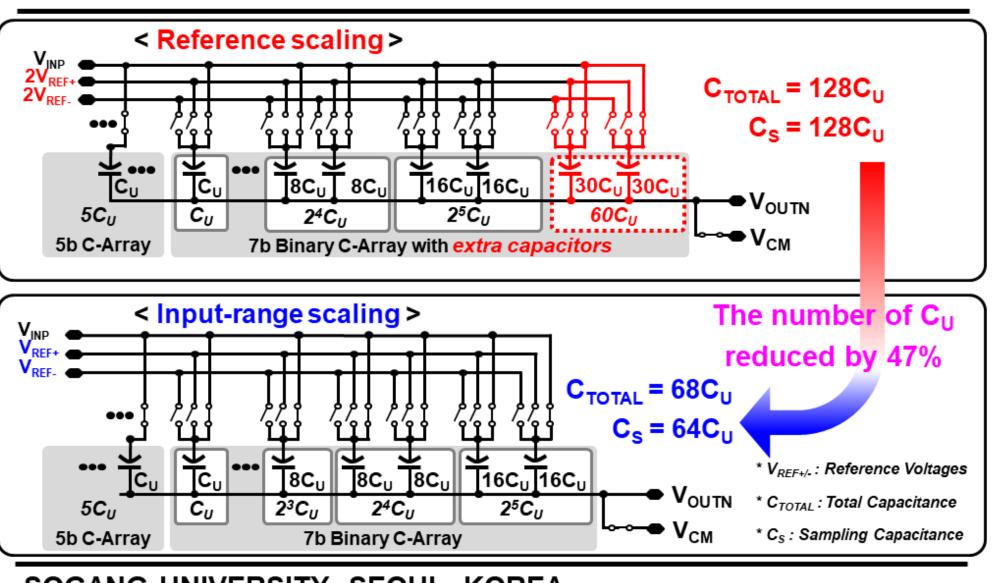

## PROPOSED INPUT-RANGE SCALING SCHEME

SOGANG UNIVERSITY, SEOUL, KOREA

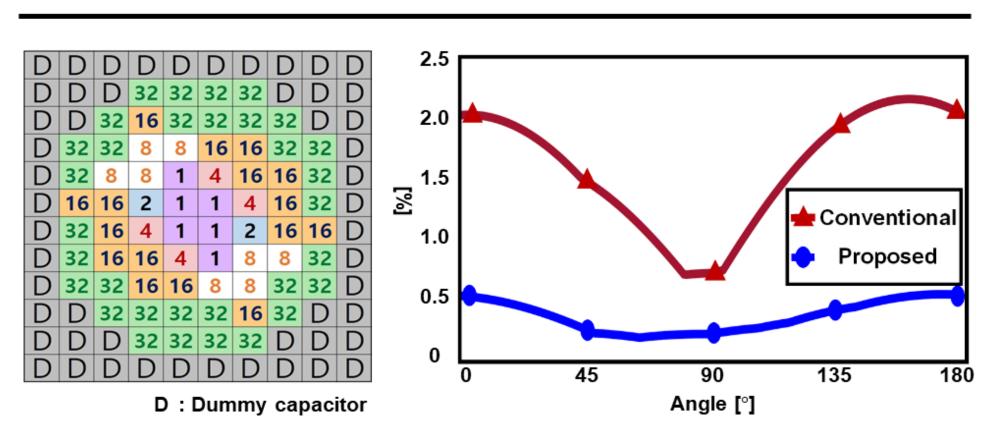

#### MISMATCH-MINIMIZED CAPACITOR PLACEMENT

- ightharpoonup More careful placement of  $\mathbf{C}_{\mathsf{U}}$  needed to minimize capacitor mismatch

- → Common-centroid placement typically used to reduce oxide-gradient-induced mismatch

SOGANG UNIVERSITY, SEOUL, KOREA

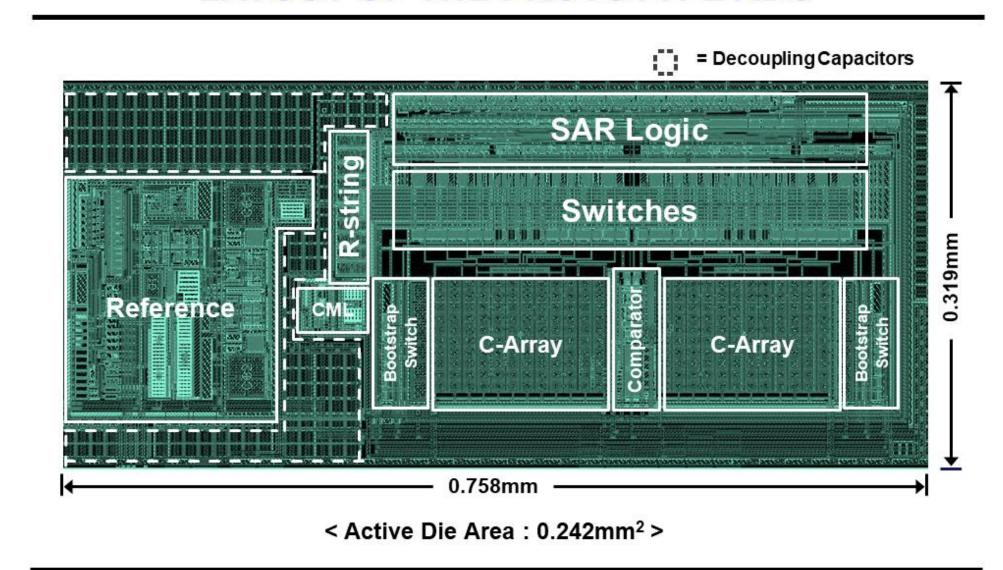

# LAYOUT OF THE PROTOTYPE ADC

SOGANG UNIVERSITY, SEOUL, KOREA

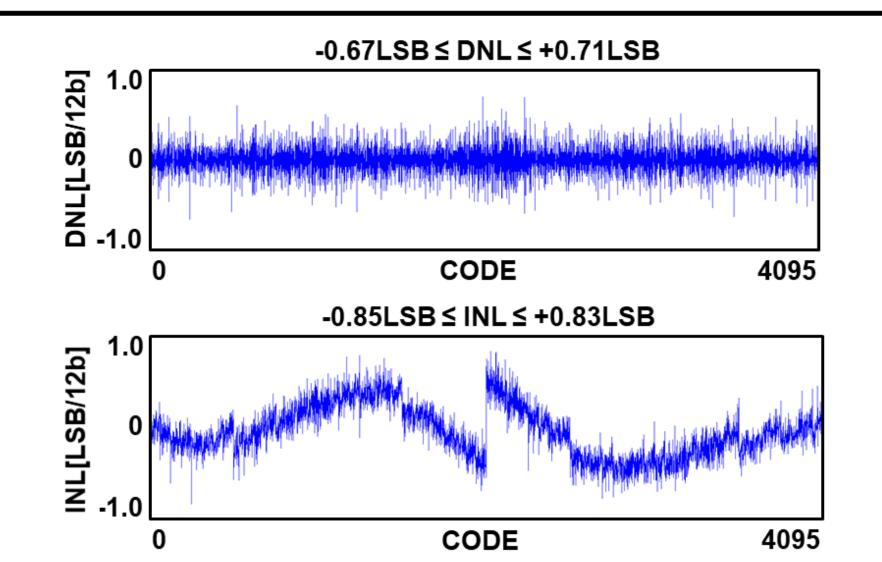

## **MEASURED STATIC PERFORMANCE**

SOGANG UNIVERSITY, SEOUL, KOREA

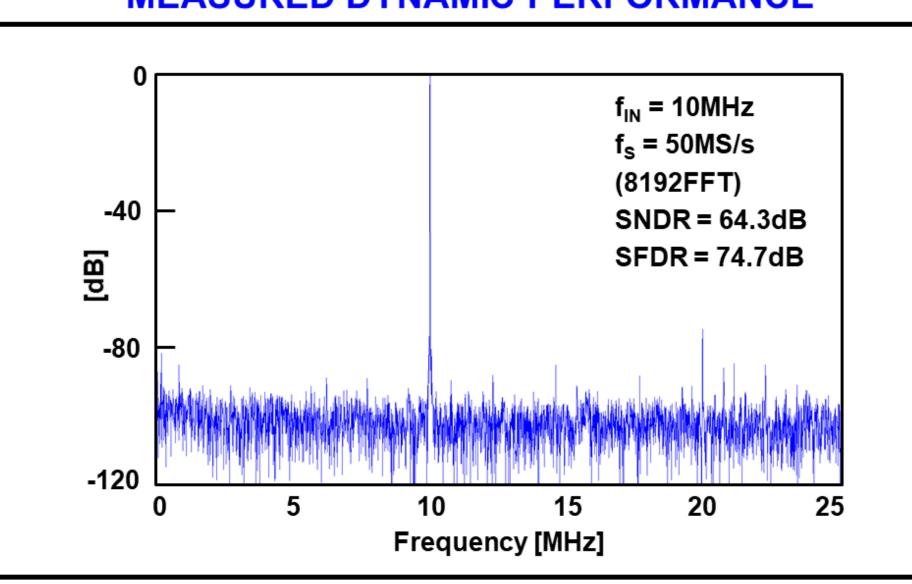

# MEASURED DYNAMIC PERFORMANCE

SOGANG UNIVERSITY, SEOUL, KOREA

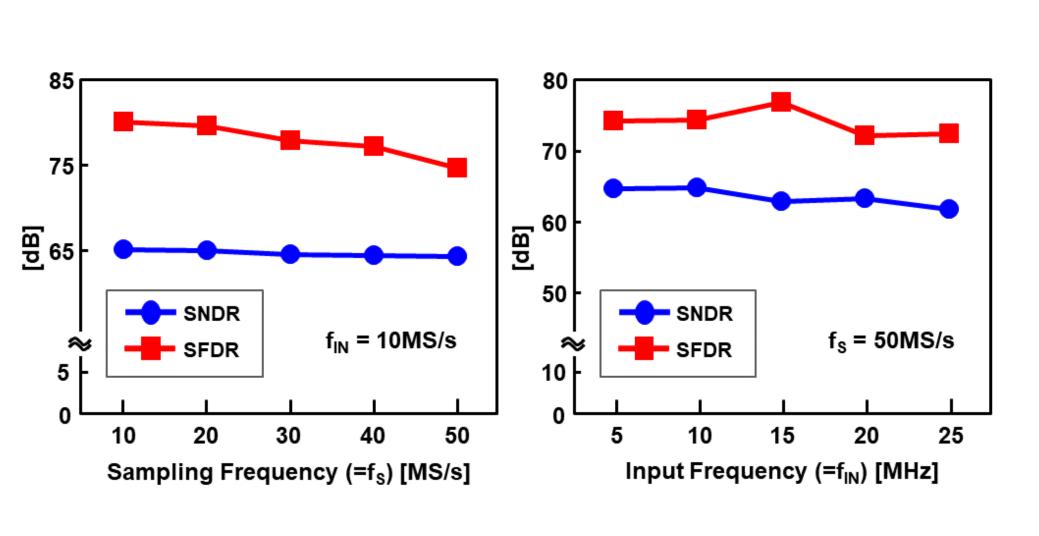

# MEASURED SNDR & SFDR vs. f<sub>s</sub> & f<sub>IN</sub>

SOGANG UNIVERSITY, SEOUL, KOREA

## MEASURED ADC PERFORMANCE

| Resolution      | 12bits                                                                  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------|--|--|--|--|

| Conversion Rate | 50MS/s                                                                  |  |  |  |  |

| Process         | MagnaChip 0.18µm CMOS                                                   |  |  |  |  |

| Supply          | 1.8V                                                                    |  |  |  |  |

| Input Range     | 1.4V <sub>P-P</sub> (differential)                                      |  |  |  |  |

| DNL             | -0.67LSB / +0.71LSB                                                     |  |  |  |  |

| INL             | -0.85LSB / +0.83LSB                                                     |  |  |  |  |

| SNDR            | 64.3dB (@ f <sub>IN</sub> = 10MHz) / 61.1dB (@ f <sub>IN</sub> = 25MHz) |  |  |  |  |

| SFDR            | 74.7dB (@ f <sub>IN</sub> = 10MHz) / 72.6dB (@ f <sub>IN</sub> = 25MHz) |  |  |  |  |

| ADC Power       | 4.74mW (w/o I/V REF) / 6.73mW (with I/V REF)                            |  |  |  |  |

| Active Die Area | 0.165mm² (w/o I/V REF) / 0.242mm² (with I/V REF)                        |  |  |  |  |

SOGANG UNIVERSITY, SEOUL, KOREA

## COMPARISON TO THE PREVIOUS ADCs

|              | Resol.<br>[bits] | Speed<br>[MS/s] | Supply<br>[V] | Power<br>[mW]<br>(@ Current) | Area<br>[mm²] | Number<br>of<br>Unit Cap. | Cal. | SNDR<br>[dB] | FoM<br>[fJ/conv.] | Process<br>[CMOS] |

|--------------|------------------|-----------------|---------------|------------------------------|---------------|---------------------------|------|--------------|-------------------|-------------------|

| This<br>Work | 12               | 50              | 1.8           | 4.74<br>(2.63mA)             | 0.17          | 136                       | X    | 64.3         | 70.6              | 0.18µm            |

| TCASI'16     | 12               | 10              | 1.8           | 0.82<br>(0.46mA)             | 0.36          | 4096                      | х    | 66.9         | 44.2              | 0.18µm            |

| APCCAS'18    | 12               | 20              | 1.5           | 1.22<br>(0.81mA)             | 0.10          | 300                       | х    | 61.7         | 59.6              | 0.18µm            |

| TCASI'18     | 12               | 20              | 1.8           | 1.77<br>(0.98mA)             | 1.61          | 2048                      | 0    | 64.6         | 63.7              | 0.18µm            |

| TVLSI'18     | 12               | 40              | 1.2           | 1.32<br>(1.10mA)             | 0.10          | 280                       | х    | 62.5         | 30.4              | 0.13µm            |

| JSSC'15      | 12               | 35              | 1.1           | 0.42<br>(0.38mA)             | 0.06          | 1024                      | 0    | 60.9         | 13.2              | 40nm              |

SOGANG UNIVERSITY, SEOUL, KOREA

2020 IDEC Congress CDC This work was supported by the IDEC.